## ESCUELA TÉCNICA SUPERIOR DE INGENIEROS INDUSTRIALES Y DE TELECOMUNICACIÓN

#### UNIVERSIDAD DE CANTABRIA

## Proyecto Fin de Carrera

# Migración de un sistema operativo de tiempo real, MaRTE OS, a un microcontrolador

Para acceder al Título de

# INGENIERO TÉCNICO INDUSTRIAL ESPECIALIDAD ELECTRÓNICA INDUSTRIAL

Autor: Alberto Gutiérrez Castro Santander, octubre de 2003 Quiero agradecerle muy sinceramente a Mario toda su ayuda y paciencia que a tenido, la ayuda que ha sido indispensable para realizar este proyecto, ha sido como una biblioteca de ayudas, y sobre todo la paciencia que ha tenido con todas y cada una de las consultas, preguntas y dudas a las que le he bombardeado continuamente.

Quisiera dar las gracias a Michael González Harbour por todo, por haberme dado la oportunidad de realizar este proyecto en el departamento, así como por su ayuda y orientación en la planificación y desarrollo del proyecto.

También quisiera agradecer y destacar el buen ambiente que se existe en el departamento de Electrónica y computadores de la facultad de Ciencias.

Y sobre todo se lo quiero agradecer a mi familia, por toda su comprensión y paciencia.

Octubre 2003

### ÍNDICE

| 0                                                            | RESUMEN                                                                                                                                                                                                   |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                            | INTRODUCCIÓN                                                                                                                                                                                              |

| 1.1<br>1.2<br>1.3                                            | SISTEMAS EMPOTRADOS DE TIEMPO REAL                                                                                                                                                                        |

| 1.4<br>1.5<br>1.6<br>1.7<br>1.8                              | EL MICROCONTROLADOR MC68332. ENTORNO DE DESARROLLO CRUZADO. PORTABILIDAD DE MARTE OS. OBJETIVOS DEL PROYECTO. ESTRUCTURA DE ESTA MEMORIA.                                                                 |

| 2                                                            | SISTEMA OPERATIVO MaRTE OS                                                                                                                                                                                |

| 2.1<br>2.2<br>2.3                                            | CARACTERÍSTICAS PRINCIPALESARQUITECTURAINTERFAZ ABSTRACTA CON EL HARDWARE                                                                                                                                 |

| 3                                                            | EL MC68332                                                                                                                                                                                                |

| 3.1<br>3.2<br>3.3<br>3.3.1<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3 | CARACTERÍSTICAS PRINCIPALES CONFIGURACIÓN SYSTEM INTEGRATION MODULE (SIM). REGISTROS DE CONFIGURACIÓN SIM. TIME PROCESSOR UNIT (TPU). ESTRUCTURA TPU. REGISTROS DE CONFIGURACIÓN TPU. INTERRUPCIONES TPU. |

| 4                                                            | MIGRACIÓN DE MARTE OS A MOTOROLA MC68332                                                                                                                                                                  |

| 4.2                                                          | DESARROLLO DE MARTE OS EN MC68332<br>ESTRUCTURA E IMPLEMENTACIÓN DE MARTE OS<br>EN MC68332                                                                                                                |

| 4.2.2                                                        | INTERRUPT_TABLESTPU                                                                                                                                                                                       |

| 4.2.3<br>4.2.4                                               | PROCESSOR_REGISTERSHARDWARE_INTERFACE                                                                                                                                                                     |

| 5                                                            | PROTOTIPO DE PLATÆFORMA DE APLICACIÓN                                                                                                                                                                     |

Octubre 2003

|                                                                                       | Y EJECUCIÓN                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                         | RoBIOS LIBRERÍA DE FUNCIONES DE PERIFÉRICOS ROBIOS & MaRTE OS HARDWARE DESCRIPTION TABLE (HDT) CONTROLADOR EyeBot DESARROLLO DE LA APLICACIÓN PROBLEMAS Y SOLUCIONES CONCLUSIONES                                                                                                                                                                                                                        |

| 6                                                                                     | ENTORNO DE DESARROLLO                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.1                                                                                   | HERRAMIENTAS DEL ENTORNO DE DESARROLLO CRUZADO                                                                                                                                                                                                                                                                                                                                                           |

| 6.2                                                                                   | INSTALACIÓN DE HERRAMIENTAS DE COMPILACIÓN CRUZADA<br>GNU C/ADA                                                                                                                                                                                                                                                                                                                                          |

| 6.3<br>6.4<br>6.5<br>6.5.1<br>6.5.2<br>6.6<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>6.7 | EJEMPLO DE APLICACIÓN C hola_mundo.c  EJEMPLO DE APLICACIÓN ADA hola_mundo.adb  DESCARGA DE APLICACIONES POR LA LÍNE A SERIE.  CONFIGURACIÓN DEL PUERTO SERIE EN LINUX.  CONFIGURACIÓN DEL SOCCERBOT.  DEPURADOR CRUZADO.  INSTALACIÓN DE DEPURADOR GDB-4.17.  COMANDOS BDMCOMMANDS, INITGDB & GDB_MARTE.  MODO DE EMPLEO DEL DEPURADOR GDB-4.17.  INSTALACIÓN DEL MÓDULO 'BDM' EN EL PC.  CONCLUSIONES. |

| 7                                                                                     | CONCLUSIONES Y TRABAJO FUTURO                                                                                                                                                                                                                                                                                                                                                                            |

| 7.1<br>7.2                                                                            | CONCLUSIONES                                                                                                                                                                                                                                                                                                                                                                                             |

| I                                                                                     | BIBLIOGRAFÍA                                                                                                                                                                                                                                                                                                                                                                                             |

#### 0 RESUMEN

MaRTE OS (Minimal Real-Time Operating System for Embedded Applications) es un sistema operativo de tiempo real conforme con el subconjunto mínimo definido en el perfil del estándar POSIX 13. El estándar POSIX ("Portable Operating System Interface") define la interfaz que los sistemas operativos deben ofrecer a las aplicaciones, así como la semántica de los servicios ofrecidos por esa interfaz. En el estándar POSIX 13 se encuentra definido el perfil "Sistema de Tiempo Real Mínimo", pensado para aplicaciones empotradas pequeñas. Dicho perfil incluye un pequeño subconjunto de toda la funcionalidad definida en el estándar POSIX, lo que permite su implementación como un núcleo de sistema operativo pequeño y suficiente. MaRTE OS no es un sistema propietario, sino que tiene una licencia GPL (General Public License) con la que todo el código fuente se encuentra disponible para el público en general.

MaRTE OS se desarrolló originalmente para el microprocesadores de la familia intel x86. Nuestra intención será la de migrar a una plataforma diferente, que deberá cumplir unos requisitos mínimos tales como: trabajar con micros de 32 bits; tener un amplio juego de instrucciones que permitan optimizar las cualidades temporales de MaRTE OS; tener una capacidad de almacenamiento de al menos 1 MB, ya que una aplicación sencilla de gestión de 2 tareas en MaRTE OS utiliza unos 250 kbytes a los que se debe añadir el software de gestión de los periféricos y las librerías que requieren su correcto funcionamiento. Además deberá soportar compiladores de alto nivel de software libre. El compilador que se utilice deberá poder compilar tanto MaRTE OS como la aplicación de desarrollo, generando un único archivo listo para ser transmitido a la plataforma deseada, y esto implica compilar para lenguajes de alto nivel tales como Ada (MaRTE OS) y C (aplicación) por lo que deberemos tener acceso a su código fuente para adaptarlo a nuestras necesidades. Teniendo en cuenta todos estos requisitos se ha elegido el microcontrolador MC68332, y se ha encontrado un producto comercial, el controlador EyeBot, que nos servirá para el desarrollo del proyecto y para hacer una demostración del funcionamiento.

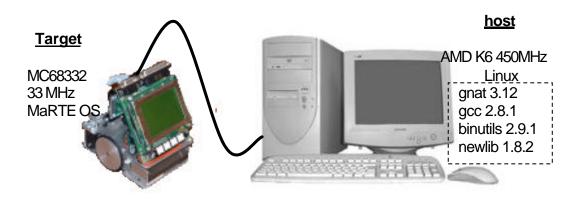

El controlador EyeBot trabaja con un potente microcontrolador MC68332 de 32 bits junto con una memoria ROM de 512 KBytes para la librería de funciones del controlador y 384 KBytes para la ejecución de programas, y una memoria RAM de 2 MBytes. Este microcontrolador está soportado por compiladores de alto nivel, y auque esta característica es esencial para la migración de MaRTE OS, conlleva la generación de un entorno de desarrollo cruzado que nos permita generar código para el MC68332, "target", en un ordenador de desarrollo PC, "host".

El objetivo principal del trabajo a realizar es el de portar MaRTE OS a la plataforma deseada. Esto implica generar un entorno de desarrollo cruzado que facilite la compilación, enlace y depuración tanto de MaRTE OS como de las aplicaciones de desarrollo que se diseñen.

El entorno de desarrollo cruzado consta de dos partes: herramientas de compilación, enlace de librerías y aplicaciones que generen un único archivo listo para ser ejecutado en la plataforma, y herramientas para la depuración de los archivos, a través del cable de comunicación entre el controlador y el PC de desarrollo.

Entre las herramientas de compilación nos basaremos en el compilador GCC adaptado para lenguajes de programación C y Ada, y unas BINUTILS cruzadas que contienen herramientas tan necesarias como son el GAS, para ensamblar el código generado en el lenguaje del microcontrolador, y el GLD, que nos permitirá enlazar todos los archivos compilados anteriormente y las librerías necesarias para generar un archivo único listo para ser ejecutado por el microcontrolador.

Para el desarrollo de una aplicación que demuestre el correcto funcionamiento del trabajo realizado, utilizamos el controlador EyeBot sobre la estructura SoccerBot, esto es, un pequeño robot con variedad de periféricos (sensores de presencia, motores, encoders, cámara digital color, LCD, etc...). El SoccerBot trabaja con RoBIOS, que es un conjunto de módulos software que nos permitirá acceder a los diferentes menús para la carga, ejecución y depuración de programas, así como de la configuración de los diferentes puertos y periféricos. Nos basaremos en los controladores y funciones que existen desarrollados e implementados en una amplia variedad de librerías que nos suministra el SoccerBot para el control de los diferentes periféricos. Así que cuando el SoccerBot ejecute una aplicación, MaRTE OS, se encargará de hacer todos los trabajos que corresponden al sistema operativo, control de tareas, temporización, etc. Y de RoBIOS utilizaremos funciones que controlen los periféricos que utilizaremos en cada una de las tareas.

Se ha realizado una pequeña aplicación que mueve el robot evitando los obstáculos que encuentra a su paso, con objeto de que sirva de demostración del trabajo realizado en el proyecto.

#### 1 INTRODUCCIÓN

Para comprender mejor el desarrollo del proyecto debemos situarnos en su contexto, por un lado analizaremos los microprocesadores y los microcontroladores, por otro lado, lo que son los sistemas de tiempo real, los sistemas empotrados donde confluyen en el concepto de "sistemas empotrados de tiempo real", como evolución necesaria y obligada, nos introducirememos en los conceptos de sistema operativo, "System on Chip" y conjunto de estándares que definan el perfil de la interfaz entre la aplicación y el sistema.

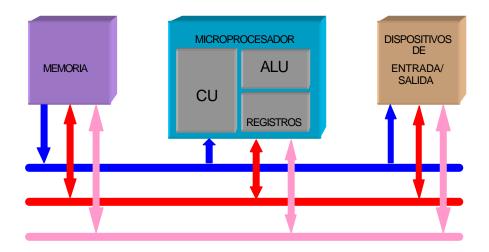

Los sistemas basados en microprocesadores son sistemas separados en unidades cuya configuración mínima se basa: CPU, memorias y dispositivos de entrada/salida; y mantienen una comunicación entre unidades a través de los difentes buses: de direcciones, de datos y de control. Con estos sistemas podemos llegar a conseguir una gran variedad de configuraciones limitados por el peso, el tamaño, el consumo o el coste.

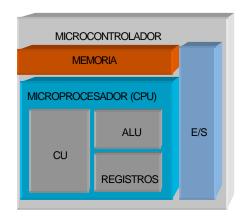

La otra opción que tenemos son los sistemas microcontroladores o sistemas cerrados, es decir, son sistemas en los que podemos encontrar la CPU, la memoria y los dispositivos de entrada/salida dentro de una misma pastilla o chips, suelen ser sistemas menos potentes pero con un menor consumo, una amplia variedad y más adecuados para sistemas empotrados, esto es, que incorporan el elemento de control dentro del propio sistema. Existe un gran nº de familias de microcontroladores que nos permitirán elegir el que más adecue a nuestra aplicación.

Muchos de los sistemas empotrados deben ser sistemas capaces de realizar tareas y responder a eventos asíncronos externos dentro de unos plazos temporales determinados que garanticen el correcto funcionamiento del sistema. Si el sistema de tiempo real lo aplicamos en un entorno empotrado manteniendo las características individuales de cada uno de los sistemas anteriores, estaremos desarrollando "sistemas empotrados de tiempo real".

#### 1.1 SISTEMAS EMPOTRADOS DE TIEMPO REAL

A menudo se clasifica erróneamente un sistema empotrado como de tiempo real. Sin embargo, los sistemas empotrados no requieren por defecto de capacidades de tiempo real.

Podemos definir un sistema de tiempo real como aquel con restricciones temporales cuyo cumplimiento garantice el correcto funcionamiento; este tipo

de sistemas son capaces de realizar tareas concurrentes y responder a eventos asíncronos externos dentro de unos plazos temporales determinados.

Podemos clasificar los sistemas de tiempo real como:

- ?? Sistemas de tiempo real estricto (Hard Real Time):

Cuando el sistema debe responder siempre a los eventos de una forma

determinista, con tiempo acctado. Un ejemplo sería el control electrónico de

estabilidad de un automóvil (ESP), que debe asegurar la respuesta dentro

de un tiempo acotado o de lo contrario la acción de control sería inútil.

- ?? Sistemas de tiempo real no estricto (Soft Real Time):

Cuando el sistema debe responder de una forma determinista, pero las

restricciones temporales son suaves siendo suficiente que el

comportamiento del sistema esté dentro de un rango de tolerancia. Por

ejemplo, sistemas de comunicación donde el retraso en la entrega de un

paquete de voz puede tolerarse descartándolo y procesando el siguiente.

Para implementar un sistema del primer tipo, necesitaremos un sistema operativo que garantice la ejecución del código generado con restricciones de tiempo real.

Los sistemas empotrados se caracterizan porque el computador constituye una parte más de un sistema mayor en el que se encuentra altamente integrado y en el que se dedica a realizar una función o un pequeño conjunto de ellas. Si este tipo de sistemas requiere capacidades de tiempo real, estaremos hablando de "Sistemas Empotrados de Tiempo Real".

Todos estos sistemas están extendiéndose rápidamente gracias a los avances tecnológicos que desarrollan procesadores más baratos y más potentes, siendo cada vez más habitual encontrarse "computadores empotrados" en productos de consumo tan habituales como televisores, juguetes, reproductores DVD, etc.

El "World Semiconductor Trade Statistics" [WSTS] en su "Blue Book" de 2002 estima que en el mundo hay 5.000 millones de sistemas empotrados en uso, con unas expectativas de ventas de 2.000 millones de unidades / año para los próximos años.

Las limitaciones mencionadas eran mucho más relevantes hace unos años, debida a una menor potencia de los microcontroladores respecto a los microprocesadores, lo que exigía reducir al máximo los tiempos de cómputo y el tamaño de las aplicaciones empotradas. En consecuencia, la mayor parte de ellas se debían escribir en lenguaje ensamblador y sin utilizar ningún sistema operativo.

#### 1.2 NECESIDAD DE UN SISTEMA OPERATIVO

Los sistemas de control demandan cada vez más servicios sofisticados que proporcionan los sistemas operativos modernos, estos son:

- ?? Interfaces gráficas de alta resolución con el usuario (GUI). (X Windows, Web, etc...)

- ?? Pilas de protocolos de red.

- ?? Sistemas de ficheros y manejadores de dispositivos.

Además, el uso de un sistema operativo nos permitirá independizar el software de la plataforma (portabilidad), utilizar el soporte del sistema operativo (herramientas), y si consideramos esto, junto con la velocidad a la que se innova el hardware (CPU, chipset) y velocidad a la que este nuevo hardware queda obsoleto, podemos concluir que, los servicios deseados no pueden ser alcanzados utilizando la aproximación "antigua" de desarrollar todo el sistema o rescribir todo el código para cada diseño empotrado.

Por tanto, la solución eficaz es incorporar en nuestro sistema empotrado un sistema operativo que nos ofrezca estos servicios, con lo que logramos independizar el código de nuestra aplicación de control, y que además nos puede ofrecer la portabilidad del sistema empotrado una vez desarrollado.

En la actualidad, las mejoras tecnológicas y el consiguiente incremento en la complejidad de las aplicaciones han hecho casi imprescindibles la utilización de lenguajes de alto nivel y sistemas operativos en la mayoría de los entornos empotrados. Así, según datos de un estudio realizado por "Venture Development Corporation" [VDC00], ya en el año 2000 el 48% de los fabricantes de sistemas empotrados utilizaban sistemas operativos comerciales, el 26% sistemas operativos propios y solamente un 26% que no utilizaba ningún sistema operativo.

En este avance también ha influido la necesidad constante de los fabricantes de sistemas empotrados de reducir tiempos de desarrollo y aumentar la fiabilidad de las aplicaciones generadas. Estas mejoras se han logrado en gran medida mediante la aplicación en el desarrollo de las aplicaciones empotradas de los aspectos más avanzados de la ingeniería software para sistemas de tiempo real, como son la programación concurrente, estrategias sofisticadas de planificación de tareas, programación orientada a objetos, etc. Tecnologías, que difícilmente hubieran podido ser aplicadas sin la utilización de lenguajes de alto nivel y sistemas operativos.

En un principio, fueron los fabricantes de los sistemas hardware los que gradualmente procedieron a incorporar algunos de estos conceptos en sus sistemas de desarrollo específicos. La consecuencia de esta acción descoordinada y casi siempre competitiva, era que se requería por parte de las

Octubre 2003

empresas un gran esfuerzo para transferir o adaptar el software a las diferentes plataformas hardware de sus controladores industriales, que por su naturaleza son en general poco homogéneas. La solución a esta problemática se está buscando en el ámbito internacional mediante la elaboración de normas de estandarización, que permiten independizar los diferentes aspectos del diseño del sistema (arquitectura hardware, software de base, sistema operativo, aplicación), consiguiendo con ello una mayor modularidad, reusabilidad y, en definitiva, una reducción del tiempo de diseño y de los costos.

Entre las normas internacionales de estandarización destaca el estándar POSIX (Portable Operating System Interface) [PSX96] [PSX01] cuyo objetivo es permitir la portabilidad de aplicaciones a nivel de código fuente entre diferentes sistemas operativos.

Con este fin, y basándose en la interfaz del extensamente utilizado sistema operativo Unix, el estándar POSIX define la interfaz que los sistemas operativos deben ofrecer a las aplicaciones, así como la semántica de los servicios ofrecidos por esa interfaz.

La interfaz descrita en el estándar permite escribir aplicaciones de tiempo real de forma portable. Sin embargo, debido al tamaño del estándar POSIX, resulta inabordable su implementación completa en un sistema operativo destinado a computadores empotrados pequeños. Por esta razón en el estándar POSIX.13 se define el "Sistema de Tiempo Real Mínimo", que está pensado para aplicaciones empotradas pequeñas. Dicho perfil incluye un pequeño subconjunto de toda la funcionalidad definida en el estándar POSIX, lo que permite su implementación en un núcleo de sistema operativo pequeño y eficiente.

Otro importante conjunto de estándares en el área de las aplicaciones de tiempo real está constituido por los lenguajes de programación. Así el C++ [C++98], y el Ada 95 [ADA95], aportan mecanismos para poder aplicar programación orientada a objetos. Ada 95 soporta los aspectos más avanzados de la ingeniería software para sistemas de tiempo real, como son la programación concurrente con tiempos de respuesta predecibles, estrategias sofisticadas de planificación de tareas y programación orientada a objetos. Su tipificación estricta permite detectar muchos problemas en tiempo de compilación, lo que incrementa considerablemente la fiabilidad del código generado.

El sistema operativo MaRTE OS está diseñado conforme con el perfil mínimo. Su estructura interna es modular y conocida de forma que, es sencillo incorporar nuevos servicios para proceder a su prueba y evaluación. Es importante destacar la fiabilidad, MaRTE OS se encuentra escrito en su mayor parte en lenguaje Ada (más una pequeña parte en lenguaje ensamblador del

MC68332), soporta la programación modular, con lo que se potencia la fiabilidad del código generado. MaRTE OS constituye una experiencia pionera, al se uno de los primeros sistemas operativos escritos en Ada que permite la ejecución de aplicaciones concurrentes escritas en C, Ada, o una mezcla de ambos.

Ciertamente existen sistemas operativos de tiempo real con interfaz POSIX cuyo código se encuentra disponible, como RTEMS [RTE03], pero el problema es que su diseño interno no sigue el modelo de 'threads' descrito en el estándar lo que, además de constituir una fuente de ineficiencia, complica la realización de modificaciones basadas en POSIX.

El sistema operativo MaRTE OS no consiste únicamente en un núcleo en el que se implementa la funcionalidad incluida en el subconjunto mínimo del POSIX, sino que además consta de una serie de aplicaciones y servicios que posibilitan la creación, carga y depuración de las aplicaciones. Ha sido necesario, por tanto, crear un entorno de desarrollo cruzado basado en Linux y en los compiladores de GNU [GNU02] GCC y GNAT.

#### 1.3 LOS MICROPROCESADORES Y LOS MICROCONTROLADORES

La plataforma que soportaba originalmente MaRTE OS antes de la realización de este proyecto, era los microprocesadores intel x86, en la que se basa este proyecto, son los microcontroladores el motorota MC68332. A continuación trataremos de describir las características de cada una de las plataformas.

Un microprocesador es un circuito integrado que ejecuta instrucciones de forma secuencial y síncrona, que necesita una tensión continua y estable que lo alimente (tensiones típicas de alimentación: 5v, 3.3v, 2.5v, 7.2v), una señal de reloj y circuitos digitales adicionales, que configuren un sistema mínimo microprocesador.

El microprocesador saca al exterior las líneas de sus buses de direcciones, datos y control, para permitir conectarlo con la Memoria y los Módulos de E/S y configurar un computador implementado por varios circuitos integrados. Se dice que un microprocesador es un sistema abierto porque su configuración y sus componentes varían de acuerdo con la aplicación a la que se destine.

El microprocesador interpreta o decodifica combinaciones de bits (órdenes) y genera señales digitales internas y/o externas para el resto de los circuitos, para así ejecutar de manera continua una secuencia de órdenes (programa).

Un sistema mínimo microprocesador estará formado por:

- ?? La Unidad Central de Proceso (CPU)

- + La Unidad de Control (CU)

- + La Unidad Aritmético-Lógica (ALU)

- + Los Registros

- ?? Memoria

- ?? Los dispositivos de entrada/salida

Figura. Sistema mínimo microprocesador

La comunicación entre unidades se realiza a través de:

- ?? Bus de direcciones (unidireccional), el número de líneas (m) nos indica la capacidad para direccionar 2<sup>m</sup> posiciones de memoria.

- ?? Bus de datos (bidireccional), para la transmisión de datos, el número de líneas del bus nos indica el número de bits capaz de transmitir en paralelo.

- ?? Bus de control, heterogéneo, depende de cada microcontrolador.

Teniendo en cuenta esta configuración básica de los microprocesadores, podemos encontrar gran variedad de configuraciones diferentes, tan sólo deberemos elegir la adecuada para la aplicación que se vaya a realizar. Las características de los microprocesadores vienen dadas por:

- ?? Tamaño de los datos que maneja

- ?? Frecuencia de trabajo

- ?? Capacidad de direccionamiento

- ?? Densidad de integración

- ?? Número de registros internos

- ?? Juego de instrucciones que maneja

- ?? Arquitectura interna y externa

Podemos clasificar los sistemas basados en microprocesadores por el tamaño de los datos que maneja, entonces encontraremos desde pequeños microcontroladores de 4 bits hasta potentes computadores con procesadores digitales de señal (DSPs), procesadores integrados de aplicación específica (ASIP) que están optimizados para una aplicación concreta o procesadores RISC de 64 bits. Sin embargo, la mayor parte de los sistemas ven limitadas sus prestaciones por razones de tamaño, peso, consumo y coste.

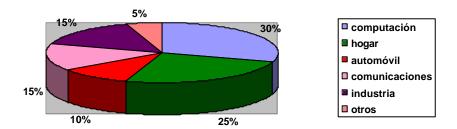

La distribución de los microprocesadores por sectores:

Las compañías diseñadoras y fabricantes de circuitos integrados desde siempre han participado en la carrera por obtener dispositivos más potentes, basando esta potencia en un aumento de los recursos internos del dispositivo. Respecto a esto último, el avance ha sido vertiginoso. En los años 80 un simple controlador de disquetera contenía más del doble de los componentes que hoy en día tiene un ordenador.

Todas las decisiones arquitecturales como RISC vs. CISR, Firmware vs. Wired, etc..., se fueron concentrando gracias al avance de la VLSI (Very Large Scale Integration), hasta llegar a ser decisiones internas a un sólo chip, ya que en el mismo, es posible encontrar recursos tales como CPU, memorias, periféricos de comunicaciones, control, potencia, interfaz, etc... Esta necesidad de integración de los sistemas microprocesadores desarrolló el microcontrolador.

El microcontrolador es un sistema cerrado. Todas las partes del computador están contenidas en su interior y sólo salen al exterior las líneas que gobiernan los periféricos.

Si sólo se dispusiese de un modelo de microcontrolador, éste debería tener muy potenciados todos sus recursos para poderse adaptar a las exigencias de las diferentes aplicaciones. Esta potenciación supondría en muchos casos un despilfarro. En la práctica cada fabricante de microcontroladores oferta un elevado número de modelos diferentes, desde los

más sencillos hasta los más poderosos. Es posible seleccionar la capacidad de las memorias, el número de líneas de E/S, la cantidad y potencia de los elementos auxiliares, la velocidad de funcionamiento, etc. Por todo ello, un aspecto muy destacado del diseño es la selección del microcontrolador a utilizar.

Aunque en el mercado de la microinformática la mayor atención la acaparan los desarrollos de los microprocesadores, lo cierto es que se venden cientos de microcontroladores por cada microprocesador.

Existe una gran diversidad de microcontroladores. Quizá la clasificación más importante sea entre microcontroladores de 4, 8, 16 ó 32 bits. Aunque las prestaciones de los microcontroladores de 16 y 32 bits son superiores a los de 4 y 8 bits, la realidad es que los microcontroladores de 8 bits dominan el mercado y los de 4 bits se resisten a desaparecer. La razón de esta tendencia es que los microcontroladores de 4 y 8 bits son apropiados para la gran mayoría de las aplicaciones, lo que hace absurdo emplear micros más potentes y consecuentemente más caros. Uno de los sectores que más tira del mercado del microcontrolador es el mercado automovilístico. De hecho, algunas de las familias de microcontroladores actuales se desarrollaron pensando en este sector, siendo modificadas posteriormente para adaptarse a sistemas más genéricos. El mercado del automóvil es además uno de los más exigentes: los componentes electrónicos deben operar bajo condiciones extremas de vibraciones, choques, ruido, etc. y seguir siendo fiables. El fallo de cualquier componente en un automóvil puede ser el origen de un accidente. [DSECUPM]

La siguiente figura muestra la estructura de un microcontrolador

La demanda actual de las empresas fabricantes de ASICs, circuitos integrados para aplicaciones específicas, se está orientando hacia el diseño de

un sistema o subsistemas en un sólo chip aplicable a electrónica de consumo, por ejemplo, telefonía celular. Estos sistemas que hoy se engloban en la sigla SoC (System on Chip) contienen a menudo circuitos analógicos, circuitos de radio frecuencia (RF) y subsistemas de señales mixtas para satisfacer la demanda en aplicaciones de electrónica de comunicaciones. [CSIC00]

Cabe destacar de la tecnología SoC como la más floreciente para los computadores basados en sistemas empotrados, que tienen la característica de poder ser programados y configurados e incluso de ser reactivos (responden a eventos en el entorno en el cual se encuentran empotrados), desarrollan información del proceso y el control de tareas, siendo a menudo invisibles para el usuario. La implementación de estos sistemas, tanto los componentes hardware como software, es una parte esencial del diseño. Según la *Informatics and Mathematical Modelling Technical University of Denmark* [IMM03]

Los SoC son en su mayor parte microcontroladores que trabajan bajo un sistema operativo para entornos empotrados. El avance de los SoC, tiene una frontera, no siendo esta funcional, sino arquitectural. Aun así, con los SoC se puede llegar a conseguir una reducción en el tamaño de los equipos del 50% al 80% respecto a las tecnologías microelectrónicas convencionales, lo que permitirá un alto nivel de integración. Por otro lado, una aplicación basada en un SoC puede consumir hasta un 60 % menos de energía respecto a las convencionales, lo que permitirá poner baterías más pequeñas o que éstas duren más tiempo. Todo ello contando además con considerables reducciones en los costes de los equipos y productos finales.

Los SoC, con el fin de abordar el problema que supone el diseño de sistemas empotrados se han caracterizado por ofrecer soluciones con una mayor capacidad de interfaz en detrimento de la capacidad de procesar o cálculo, esto es, mediante el uso del microcontrolador más adecuado a la aplicación a desarrollar.

#### 1.4 EL MICROCONTROLADOR MC68332

En la elección del microcontrolador se ha optado por el MC68332 ya que contiene un microprocesador de 32 bits, que trabaja a una frecuencia de 33 MHz, tratándose de un microcontrolador de alta densidad de integración desarrollado con la tecnología metal-óxido semiconductor (HCMOS). Tiene un alto desarrollo en el manejo de datos con poderosos subsistemas periféricos a través del Bus de Comunicación entre Módulos (IMB). Además es un microcontrolador de la familia motorola 68300 de controladores empotrados de 32 bits, con muchas características de los MC68010 y del MC68020, esto es, compatible con la familia M68000.

El IMB es el encargado de la interconexión de los módulos SIM, TPU y QSM con la CPU32 (el microprocesador), entre otras características el módulo SIM, que es el modulo integrado del sistema, se encargará de la configuración y protección del sistema, el módulo TPU, la Unidad Procesadora del Tiempo, que dispone de 16 canales de propósito general para el manejo de funciones de tiempo y el módulo QSM, Módulo de Cola de Periféricos Serie, que es el encargado de facilitar la interconexión de más periféricos o comunicación entre procesadores.

El microcontrolador dispone de una memoria ROM de 512 KBytes (128 Kbytes para la librería de funciones del controlador, y 384 Kbytes para la ejecución de programas) y una memoria RAM de 2 MBytes, memoria suficiente para desarrollar con éxito nuestra aplicación.

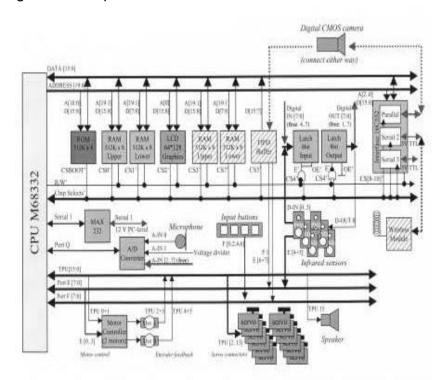

El MC68332 con el que hemos trabajado se encuentra integrado en el controlador Eyebot, elemento de control de la plataforma de desarrollo SoccerBot.

En el SoccerBot podemos encontrar 1 puerto paralelo, 3 puertos serie, 8 entrados digitales, 8 salidas digitales, 8 entradas analógicas, una cámara digital, un LCD de gráficos, un micrófono, 2 motores DC y sus servos, 6 sensores de posición por infrarrojos, el módulo de depuración (BDM) y cable para conectarlo al 'Host', puerto de infrarrojos, micrófono, speaker y golpeador.

La facilidad de programación del un microcontrolador es una importante característica a destacar. Dispone de ocho registros de datos multifunción y siete registros de direcciones de propósito general. Los registros de datos soportan datos de 8 bits (tamaño byte), 16 bits (tamaño word) y 32 bits (tamaño longword) como longitud de la palabra para todas las operaciones. Aunque el 'contador del programa' (PC) y el 'puntero de la pila' (SP) son registros de propósito especial, también se encontrarán disponibles para la mayoría de los direccionamientos. Facilidad de programar el chequeo y diagnosis mediante las instrucciones 'trace&trap'.

Como las aplicaciones en el controlador pueden llegar a extenderse y volverse bastante complejas, la el MC68332 es capaz de trabajar con compiladores para lenguajes de alto nivel, característica básica para poder desarrollar el proyecto.

A la hora de programar el microcontrolador, hay que tener en cuenta que podemos encontrarnos en dos estados de privilegio, como usuario y como supervisor, para la implementación de MaRTE OS en el microprocesador, deberemos encontrarnos en el modo supervisor, en cambio, cuando realicemos la aplicación bastará con encontrarse en el modo usuario.[MCPU]

#### 1.5 ENTORNO DE DESARROLLO CRUZADO

Uno de las características del sistema operativo MaRTE OS es que su código fuente debe estar accesible para cualquier usuario, de un modo más preciso, se trata de software abarcado por General Public License (GPL)[GNU02], esto es un conjunto de específico de términos de distribución para proteger un programa de 'software libre'. Software libre se refiere a la libertad de los usuarios para ejecutar, copiar, distribuir, estudiar, cambiar y mejorar el software. Para que las libertades de hacer modificaciones y de publicar versiones mejoradas tengan sentido, debemos tener acceso al código fuente del programa. Por lo tanto, la posibilidad de acceder al código fuente es una condición necesaria para el software libre.

El software libre debe su impulso y creación a la Fundación para el Software Libre (FSF)[GNU02], que está dedicada a eliminar las restricciones sobre el copiado, redistribución, entendimiento, y modificación de programas de computadoras, promocionando el desarrollo y uso del software libre en todas las áreas de la computación, pero muy en particular en el proyecto GNU.

Linux es un sistema operativo derivado de UNIX desarrollado originalmente por Linux Torvals asistido por la comunidad de desarrolladores a lo largo de todo el mundo a través de Internet. Amparado bajo la licencia pública, GNU General Public License (GPL), todo el código fuente está disponible para el público en general y podemos recalcar las siguientes características:

- ?? Altamente probado y estable.

- ?? Código público GPL.

- ?? Desarrollado en C, lo que lo hace altamente portable.

- ?? Basado en el compilador GNU C, lo que permite utilizar una gran cantidad de herramientas de desarrollo.

- ?? Disponible para sistemas Intel PC.

- ?? Soporte de gran número de periféricos.

- ?? Muy documentado (Linux Documentation Project)

MaRTE OS tiene una licencia GPL, tendremos acceso al código fuente, trabajaremos también con herramientas desarrolladas en el proyecto GNU, como son los compiladores GCC y GNAT, compiladores de alto nivel de lenguajes C y Ada, las BINUTILS, conjunto de utilidades que ayudan en la compilación y la NEWLIB, que son un conjunto de librerías C.

La ventaja de trabajar con estas herramientas es que está probada sobradamente su fiabilidad, debido a su amplia utilización, además el conocimiento del código fuente sin restricciones nos deja la posibilidad de adaptarlas y modificarlas de la forma que más convenga.

Buscaremos la configuración más adecuada para nuestro propósito, e incluso, una vez se adquiera un conocimiento sobre las herramientas que generen el entorno de desarrollo, se deberá buscar la versión más adecuada que permita el mejor acoplamiento entre ellas, aplicando 'parches' y modificando los *Makefile*, que son unos pequeños archivos con permiso de ejecución, que utilizaremos para ejecutar una serie de instrucciones de

Una peculiaridad de los sistemas empotrados es la falta de un interfaz con el usuario y/o programador, por lo que para desarrollar cualquier clase de aplicación o simplemente acceder al control del microcontrolador directamente en la máquina. Se hace necesario generar un entorno de desarrollo cruzado que permita el control deseado sobre el microcontrolador.

Un entorno de desarrollo cruzado estará formado por una parte hardware y otra software, en la parte hardware encontraremos el 'host' máquina que tendrá instalada el compilador y depurador cruzados, teniendo como misión generar código para el microcontrolador o plataforma de desarrollo. El compilador cruzado se hace necesario ya que la plataforma de desarrollo por sí misma no podría entender una aplicación escrita en un lenguaje de alto nivel. Cabe otra posibilidad, y es que si la plataforma de desarrollo tuviera una interfaz con el usuario, este debería ser capaz de programar en el lenguaje de la máquina de desarrollo.

El 'host' será una máquina que trabaje con un sistema operativo (Linux, en nuestro caso) que soporte las herramientas necesarias para poder generar el código para la plataforma de desarrollo. Herramientas tales como compilador de ada *gnat*, el compilador *gcc*, las herramientas *binutils* y las librerías *newlib*. La idea será compilar código en lenguaje Ada o C (también podremos utilizar

ensamblador) basándonos en un correcto uso de: las herramientas de las binutils y las librerías suministradas por las newlib, para generar código binario en un formato entendible para la plataforma de desarrollo (file.hex),es decir, un compilador cruzado y depurador cruzados con los que podemos compilar una aplicación escrita en lenguaje de alto nivel (Ada o C) o en lenguaje ensamblador, y enlazarla con las librerías necesarias (librerías propias del SoccerBot) para la obtención de un archivo listo para ejecutar en la plataforma de desarrollo.

El depurador cruzado servirá para corregir los errores (tanto de compilación como de ejecución) y poder continuar con la depuración sin necesidad de compilar, enlazar y descargar el programa o aplicación otra vez.

Una vez que tengamos las herramientas que nos permitan obtener archivos para el MC68332, tendremos que preparar a éste para que trabaje bajo el sistema operativo deseado: MaRTE OS.

El núcleo de MaRTE OS se encuentra escrito en tres lenguajes: Ada, C y ensamblador (en el hardware\_interface y en alguno de sus paquetes). El compilador cruzado deberá entender los paquetes escritos en estos lenguajes y generar para cada uno de ellos un 'object file' (\*.o), que uniremos a las librerías estándar adecuadamente compiladas para el MC68332 (para cada uno de los archivos de las librerías también se generarán \*.o, aunque los podremos encontrar librerías compiladas para esta máquina, con la forma \*.a).

Esto se puede hacer gracias a las características del sistema operativo MaRTE OS, por las que en el computador de desarrollo (host), la aplicación es compilada y posteriormente enlazada con las librerías que forman el núcleo de MaRTE OS. El ejecutable así generado constituye un programa independiente listo para ser cargado en el microprocesador del sistema empotrado.

#### 1.6 PORTABILIDAD DE MaRTE OS

En MaRTE OS, en el núcleo se incluye una interfaz abstracta de bajo nivel para acceder al hardware. En ella se define la visión que del hardware tienen las partes del núcleo que son independientes de la plataforma de ejecución. Esta interfaz constituye la única parte del núcleo que es dependiente del hardware, lo que facilita el portado de MaRTE OS a distintas plataformas.

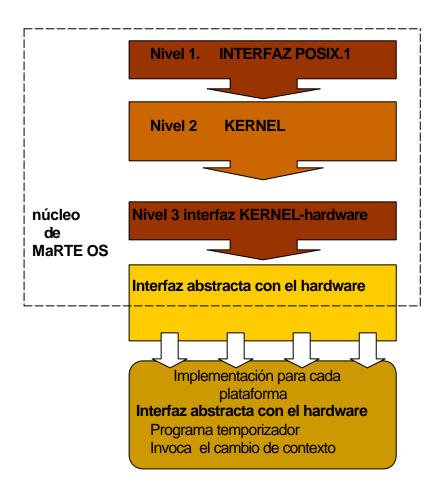

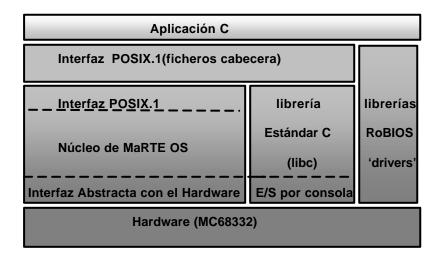

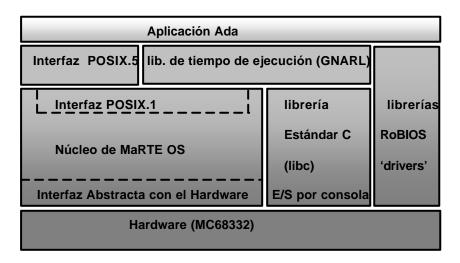

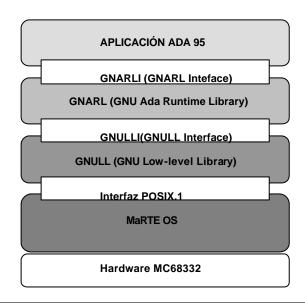

La siguiente figura nos muestra la estructura de niveles del núcleo de MaRTE OS:

La figura constituye una representación esquemática de la arquitectura interna del núcleo de MaRTE OS. Podemos diferenciar tres niveles, el *nivel 1* corresponde a la parte de la interfaz POSIX.1 aportada por el núcleo, que corresponde a los ficheros cabecera C de sus mismos nombres, los citados paquetes están constituidos en su mayor parte por renombrados de las funciones y subtipos de los tipos definidos en los paquetes del núcleo que

implementan la interfaz POSIX. El nivel 2, contiene los paquetes que componen el núcleo están organizados jerárquicamente a partir del paquete raíz *kernel*, en el que se definen los tipos, constantes y operaciones básicas que serán utilizados por el resto del núcleo. Existe un nivel 3, que será el que se encuentre más relacionado con la interfaz abstracta del hardware, será el nivel que se encargue de la funcionalidad básica del núcleo, encargado de la gestión directa de las tareas y los eventos temporales, siendo desde este nivel desde donde se realizaran las llamadas para la programación del temporizador hardware y las llamadas a la rutina de cambio de contexto.

Por lo tanto, teniendo en cuenta la estructura interna de MaRTE OS, para que el sistema operativo sea portado de una plataforma a otra, tan sólo deberemos adaptar los paquetes que se definen en la interfaz abstracta del hardware a la plataforma en la que queremos implementar MaRTE OS, manteniéndose los paquetes correspondientes al núcleo inalterados.[MAR02]

#### 1.7 OBJETIVOS DEL PROYECTO

Los objetivos de este proyecto son:

- ?? Desarrollo del entorno de desarrollo cruzado para el MC68332 Adaptados según nuestras necesidades, comenzando con la creación de un entorno de desarrollo simple, capaz de generar código para el MC68332, compilando programas codificados en lenguaje C, lo ampliaremos para que sea capaz de codificar programas escritos en Ada, y en la última evolución haremos que las aplicaciones que implementen alguna de las características POSIX de MaRTE OS, mediante el correcto enlazando con las diferentes librerías y paquetes propios de MaRTE OS.

- Adaptación de un compilador cruzado para que soporte aplicaciones escritas en lenguaje Ada y C.

- Adaptación de un depurador cruzado para el MC68332.

#### ?? Migración de MaRTE OS al MC68332

La Interfaz Abstracta con el Hardware proporciona al resto del núcleo de MaRTE OS una visión abstracta de la plataforma y debe de constar de los siguientes elementos: temporizador hardware, un reloj que permita leer y modificar la hora actual, un dispositivo que permita la habilitación o deshabilitación de interrupciones de forma individual o conjunta, operaciones de cambio de contexto, así como operaciones de conversión de tiempos. Este es precisamente el objetivo principal del presente trabajo, demostrar que esta portabilidad es posible.

- Implementación de la Interfaz Abstracta con el Hardware en el MC68332. Identificará la plataforma para la cual se encuentra versionado MaRTE OS.

- Generación de un conjunto de utilidades que automaticen la compilación, enlazado y carga de aplicaciones que utilizan MaRTE OS en MC68332.

Adaptaremos algunas herramientas proporcionadas por MaRTE OS para este propósito.

- ?? Desarrollo de una aplicación de demostración que implemente alguna de las características POSIX de MaRTE OS sobre la plataforma SoccerBot.

Antes de la aplicación de demostración se demostrará el correcto funcionamiento de MaRTE OS en el controlador EyeBot compilando y ejecutando los diferentes ejemplos proporcionados por MaRTE OS.

La aplicación trabajará con tareas concurrentes con diferentes prioridades implicando diferentes periféricos del SoccerBot de tal manera que no con su correcto funcionamiento quedará probada la viabilidad de este proyecto.

#### 1.8 ESTRUCTURA DE ESTA MEMORIA

En el capítulo 2 se hace una introducción a sistema operativo MaRTE OS, comentando las principales características, donde descubriremos la posibilidad de portado a diferentes plataformas gracias a su implementación como un núcleo con estructura monolítica. En la estructura hay una descripción de los diferentes niveles estructurales, desde la aplicación hasta, nivel más alto, hasta el hardware de la plataforma, nivel más bajo. El capítulo finaliza con una descripción de los diferentes componentes de la interfaz abstracta con el hardware, que serán requisitos mínimos indispensables comunes a cualquier plataforma elegida.

En el capítulo 3 hablamos del microcontrolador MC68332, características principales, estructura, veremos una descripción y configuración de los principales registros tanto del módulo SIM, como del TPU.

En el capítulo 4, una vez conocido el sistema operativo que se va a portar y la plataforma que lo va a recibir, se plantea como será la nueva interfaz abstracta con el hardware con los diferentes paquetes que completarán su implementación.

En el capítulo 5, utilizando el software de control de periféricos en de la plataforma de aplicación y ejecución se desarrolla la aplicación de demostración que trabaje con el sistema operativo MaRTE OS.

En el capítulo 6, se trata el entorno de desarrollo, su justificación e instalación. Encontraremos también ejemplos de aplicación para probar el correcto funcionamiento del compilador cruzado y depurador cruzado, así como la configuración de los diferentes puertos de comunicación del PC y del SoccerBot.

Terminaremos en el capítulo 7 con conclusiones y trabajo futuro.

#### 2 SISTEMA OPERATIVO Marte OS

MaRTE OS [MaR03] (Minimal Real-Time Operating System for Embedded Applications) es un sistema operativo de tiempo real conforme con el subconjunto mínimo definido en el estándar POSIX 13 desarrollado en el Departamento de Electrónica y Computadores de la Universidad de Cantabria.

Son muchos los sistemas operativos de tiempo real que proporcionan a las aplicaciones una interfaz POSIX, pero la mayoría son sistemas propietarios para los cuales no es posible disponer de su código fuente. Ciertamente existen sistemas operativos de tiempo real cuyo código se encuentre disponible, como RTEMS, RT-Linux, y entre otros, pero el problema es que en todos los casos su diseño interno no sigue el modelo de 'threads' POSIX, lo que complica la realización de modificaciones basadas en POSIX, además de constituir una fuente de ineficiencia a la hora de usar las interfaces estándar.

El lenguaje en el que está implementado de forma eficiente es el sistema operativo es Ada95.

MaRTE OS no consiste únicamente en un núcleo en el que se implementa la funcionalidad incluida en el subconjunto mínimo del POSIX (concurrencia, sincronización, temporización, etc), sino que además consta de una serie de aplicaciones y servicios que posibilitan la creación, carga y depuración de aplicaciones. Se dispone por tanto a crear un entorno de desarrollo cruzado basado en Linux y en los compiladores de GNU GCC y GNAT. [MAR02]

#### 2.1 CARÁCTERÍSTICAS PRINCIPALES

En sistemas los sistemas empotrados de tiempo real el número de 'threads' y demás recursos que precisará la aplicación en el tiempo de ejecución es limitado y conocido de antemano. Durante la configuración del sistema es posible especificar el número máximo de recursos de cada tipo que serán prealojados durante la inicialización del sistema. De esta forma es posible ajustar el tamaño del ejecutable en función de las necesidades de cada aplicación. Esto se encontrará implementado dentro de 'configuracion\_parameters.ads, como veremos más adelante. Así, entre otros parámetros es posible ajustar:

El máximo número de 'threads' que pueden existir al mismo tiempo

El número de niveles de prioridad diferentes

La longitud máxima de la cola de eventos temporales

El número máximo de temporizadores

El número máximo de señales pendientes

El número de datos específicos de cada 'thread' El tamaño de los 'stacks' de los 'threads' El número máximo de 'threads' con política de servidor esporádico El tamaño del área de memoria dinámica

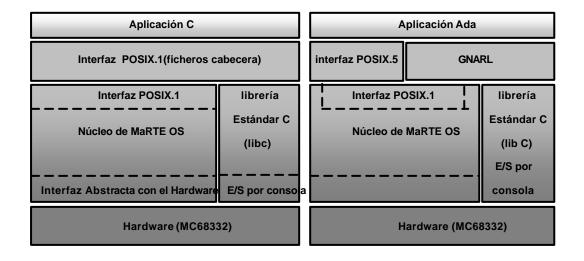

Permite ejecutar aplicaciones Ada y C.

El núcleo presenta las interfaces POSIX Ada y C. El entorno de desarrollo permite el desarrollo cruzado de aplicaciones Ada y C utilizando los compiladores de GNU GNAT y GCC.

El compilador GNAT debe implementar toda la semántica propia de las tareas Ada en su librería de tiempo de ejecución GNARL (GNU Ada Runtime Library). La librería de tiempo de ejecución es en su mayor parte independiente de la plataforma sobre la que se ejecuta. Sólo una pequeña parte, denominada GNULL (GNU Low-level Library), debe ser modificada para adaptarse a las diferentes plataformas de ejecución.

#### Portable a distintas arquitecturas

El núcleo presenta una interfaz abstracta con el hardware que permite independizar su funcionamiento del hardware específico sobre el que se ejecuta. Dicha interfaz proporciona al núcleo operaciones que permiten acceder al reloj y al temporizador del sistema, instalar manejadores de señal y realizar el cambio de contexto entre tareas. Éste es precisamente el objetivo principal del presente trabajo, demostrar que esta portabilidad es posible.

#### Núcleo monolítico

Las estructuras de datos del kernel deben ser protegidas ante la posibilidad de acceso simultáneo por parte de varias tareas ejecutando llamadas al sistema. Para lograr esa protección, MaRTE OS ha sido implementado como un núcleo con estructura monolítica, deshabilitándose las interrupciones durante los periodos de tiempo en los que se precisa acceder a estructuras globales.

Toma la forma de una librería para ser enlazada con la aplicación

En el computador de desarrollo la aplicación de usuario es compilada y posteriormente enlazada con las librerías que forman el núcleo de MaRTE OS. El ejecutable así generado constituye un programa independiente listo para ser cargado en el computador empotrado y comenzar la ejecución de usuario de forma automática. Puesto que MaRTE OS está pensado para sistemas empotrados pequeños en los que lo normal es que no exista terminal para interfaz con el usuario, no tiene sentido el disponer de ningún tipo de intérprete de comandos, cuya inclusión aumentaría el tamaño del ejecutable, según la

tesis doctoral "planificación de tareas en sistemas operativos de tiempo real estricto para aplicaciones empotradas" de Mario Aldea Rivas [MAR02]

#### 2.2 ARQUITECTURA

Visión general

El núcleo de MaRTE OS, para la implementación del núcleo en el PC, ha sido escrito principalmente utilizando el lenguaje de programación Ada 95, habiéndose utilizado también los lenguajes C y ensamblador. El uso de estos dos últimos lenguajes representa un porcentaje muy pequeño del tamaño total del núcleo, y corresponde principalmente a código tomado de otros sistemas operativos o librerías de código libre, tales como Linux, RT-Linux y el conjunto de librerías para desarrollo de sistemas operativos denominado OSKit. El lenguaje C, entre otros usos, es utilizado para el código encargado de la inicialización del PC, de la salida de caracteres por consola mediante la escritura directa en la memoria de vídeo. Así mismo durante la inicialización del sistema y para operaciones de muy bajo nivel como la rutina de cambio de contexto.

El núcleo incluye una interfaz abstracta de bajo nivel para acceder al hardware. En ella se define la visión del hardware que tienen las partes del núcleo que son independiente de la plataforma de ejecución. Esta interfaz constituye la única parte del núcleo que es dependiente del hardware, lo que facilita el portado de MaRTE OS a distintas plataformas. Además de la dependencia de la plataforma encapsulada en la interfaz abstracta con el hardware, también la librería estándar C depende del hardware sobre el que se ejecuta en lo referente a las operaciones de entrada/salida por consola. La E/S

por consola no está incluida dentro de la interfaz abstracta con el hardware porque no es común a todas las posibles arquitecturas (los sistemas empotrados normalmente no disponen de dispositivos de interfaz con el usuario). Lo normal es que esta funcionalidad sea aportada por el código encargado de manejar el dispositivo que se desea haga las veces de consola. [MAR02]

#### 2.3 INTERFAZ ABSTRACTA CON EL HARDWARE

Esta interfaz proporciona al resto del núcleo de MaRTE OS una visión abstracta de la plataforma que consta de los siguientes elementos:

Temporizador: dispositivo que permite ser programado para provocar una interrupción cuando transcurra el intervalo de tiempo elegido, siendo el intervalo máximo programable finito y conocido por MaRTE OS. Cuando el intervalo deseado supera el máximo, el núcleo se encargará de programar varias veces consecutivas el temporizador hasta cubrir dicho intervalo. Tras la inicialización del sistema el temporizador no se encuentra programado.

Reloj: dispositivo que permite leer y modificar la hora actual. No se le exige que desde la inicialización del sistema marque la hora absoluta o tiempo transcurrido desde la "época", pero sí que debe tener capacidad para almacenar una fecha de este tipo, de forma que le pueda ser asignada a posteriori. Conviene que tenga una resolución igual o mayor que la del temporizador y no es necesario que exista como dispositivo físico. En el caso de que el sistema carezca de reloj, MaRTE OS realizará la programación periódica del temporizador incluso cuando no haya ningún evento temporal pendiente. De esta forma la capa de interfaz podrá llevar la cuenta del tiempo transcurrido actualizando una variable global tras cada programación. La hora actual en un instante dado se podrá obtener como la hora de la última programación más el estado de la cuenta del temporizador en ese instante.

Operaciones de conversión de tiempos: se proporcionan operaciones que permiten convertir tiempos medidos en cuentas del reloj a valores del tipo duration y viceversa. MaRTE OS utiliza internamente el formato usado por el reloj para representar el tiempo. Se prefiere utilizar las unidades del reloj en lugar de las del temporizador puesto que las operaciones matemáticas en las que interviene el valor actual del reloj son muy frecuentes con lo que se evitan innecesarias conversiones de tipo.

Interrupciones hardware: existen una o más fuentes de interrupciones hardware identificadas en la interfaz, debiendo existir como mínimo la correspondiente al temporizador. Se facilita una operación que permite asociar un procedimiento con una interrupción de forma que sea ejecutado inmediatamente cada vez que ésta se produzca. Por defecto a todas las

interrupciones les es asignado un manejador que indica al usuario la interrupción producida y finaliza la aplicación.

Dispositivo controlador de las interrupciones: permite la habilitación o deshabilitación de las interrupciones de forma individual o conjunta. En el caso de que no exista un dispositivo que centralice el control de todas las interrupciones las operaciones de habilitación o deshabilitación actuarán, siempre que sea posible, directamente sobre los dispositivos generadores de interrupciones. El dispositivo comienza con todas las interrupciones deshabilitadas.

Cuando las operaciones del núcleo son invocadas desde un manejador de interrupción deben retrasar la ejecución de los cambios de contexto hasta después de que haya sido completado correctamente el ciclo de reconocimiento de la interrupción, con la consiguiente rehabilitación del dispositivo controlador de interrupciones. La interfaz abstracta con el hardware proporciona una operación para saber cuándo se está ejecutando dentro de un manejador y otra para indicar cuándo se desea que sea llamada la función de planificación una vez rehabilitada la interrupción en el controlador.

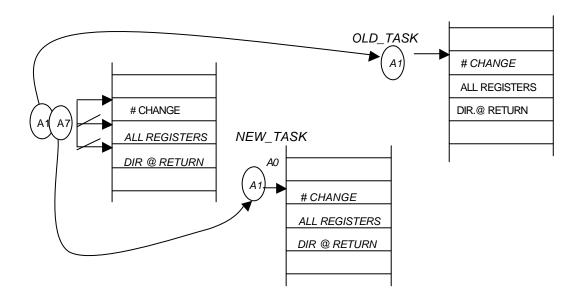

Operación de cambio de contexto entre tareas: toma como argumentos las cimas de las pilas de las tareas entre las que se realizará el cambio. Tras su ejecución el estado de los registros del procesador de la tarea saliente queda almacenado en su pila, de forma que el valor correspondiente a su contador de programa corresponde a una dirección interna de la propia rutina de cambio de contexto. Por otro lado, el estado de la tarea entrante ha sido restaurado.

Registros del procesador: existen operaciones para lectura y escritura del registro de estado del procesador. También se proporcionan operaciones para habilitar o deshabilitar todas las interrupciones mediante la modificación de uno o más bits de ese registro. Estas operaciones son más rápidas que las proporcionadas por el dispositivo controlador de interrupciones. Las operaciones sobre los registros son utilizadas por el núcleo para crear secciones críticas: la entrada a una de estas secciones se realiza almacenando el registro de estado y deshabilitando las interrupciones, mientras que la salida consiste en restaurar el antiguo valor del registro de estado. [MAR02]

En el capítulo 4 se explicará en detalle la implementación del la interfaz abstracta del hardware para el microcontrolador MC68332.

#### 3 EL MC68332

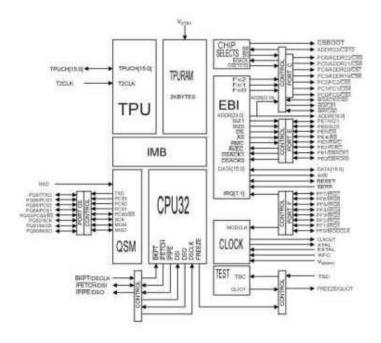

El MC68332 [MCPU], un microcontrolador de alta integración de 32 bits, combina alto rendimiento en la manipulación de datos con unos poderosos subsistemas periféricos. El microcontrolador está formado por módulos estándar y se controlan a través de un interfaz, el 'common intermodule bus' (IMB). La estandarización facilita un rápido desarrollo de dispositivos confeccionados para aplicaciones específicas.

El microcontrolador incorpora una CPU de 32 bits (CPU32), un 'System Integration Module' (SIM)[SIMRM], un 'Time Processor Unit' (TPU)[TPURM], un 'Queued Serial Module' (QSM), y un módulo de tamaño de 2 Kbytes de RAM estática con capacidad para emular la TPU (TPURAM) [TPURAM].

El microcontrolador puede incluso sintetizar una señal interna de reloj desde una referencia externa o si se usa una entrada de reloj externo directamente. La frecuencia de la señal de referencia es estándar y de valor 32.768 KHz. El hardware y el software permiten cambios en la frecuencia del reloj mientras se encuentra en uso. Porque la operación en el microcontrolador es completamente estática, los contenidos del registro y memoria no son afectados por los cambios en la frecuencia del reloj.

La alta densidad complementaria a una arquitectura metal-oxido semiconductor (HCMOS) provoca un bajo nivel de consumo de energía. Aún así, este puede ser minimizado mediante la parada del reloj del sistema. La CPU32 incluye una instrucción que implementa con eficiencia esta capacidad (LPSSTOP), 'low-power stop'.

#### 3.1 CARACTERÍSTICAS PRINCIPALES

- Unidad Central de Proceso (CPU32)

- arquitectura de 32 bits

- implementación de memoria virtual

- manejador de excepciones para aplicaciones del controlador

- soporte para lenguajes de alto nivel

- modo depuración en segundo plano

- operación completamente estática

- Módulo de Integración de Sistema (SIM)

- soporte para bus externo

- salidas programables para el chip-select

- lógica de protección del sistema

- watchdog time, clock monitor y bus monitor

- 2 puertos de 8 bits de entrada/salida de función dual

- 1 puerto de 7 bits de salida con función dual

- · Unidad de Procesado del Tiempo (TPU)

- capacidad de operación independiente de la CPU32

- 16 canales y pins independientes y programables

- algún canal puede desempeñar alguna función de tiempo

- 2 registros de cuenta de temporizador con prescalers programables

- nivel de prioridad de los canales seleccionables

- Módulo de Cola de Periféricos Serie (QSM)

- interfaz de comunicación serie mejorada

- interfaz para la cola de periféricos serie

- 1 puerto de 8 bit de función dual

En la figura: diagrama de bloques del MC68332.

#### 3.2 CONFIGURACIÓN

A continuación se detallan los registros de configuración de los módulos SIM y TPU, así como los diferentes registros que se utilizarán para la adaptación de MaRTE OS al microcontrolador. Los registros de configuración, tanto de la SIM como de la TPU, se analizarán con los valores que mantienen cuando se hace un 'reset' en el SoccerBot, esto es, los valores predeterminados que establece RoBIOS.[TB03]

#### 3.3 System Integration Module (SIM)

El módulo SIM lo forman cinco bloques funcionales que controlan el sistema de control de arranque, inicialización, configuración y bus externo. Hablaremos con detenimiento del bloque funcional de configuración, que será el que nos interese dentro de la SIM. A continuación hacemos una pequeña descripción de cada uno de los bloques.

El sistema de configuración y bloque de protección controla la configuración y el modo de operación.

El reloj del sistema genera señales de reloj utilizadas por el SIM, otros módulos IMB, y recursos externos. Por ello, un generador de interrupciones periódicas soporta el control de rutinas de tiempo de ejecución crítico.

El interfaz de bus externo maneja la transferencia de información entre los módulos IMB y el espacio de direcciones externo.

El bloque de selector de chip (chip-select) produce once señales 'chip-select' de propósito general y una 'boot ROM'. Ambos de encuentran asociados al registro base de direcciones (Base Address Register) y a los Registros de Opciones (options registers).

El bloque de test del sistema incorpora el hardware necesario para testear el microcontrolador.

El mapa de direcciones de registros de control del SIM ocupa 128 bytes. Los registros que dentro de este mapa no son utilizados devuelven ceros cuando son leídos. El bit SUPV en el registro SIMCR nos indicará en que modo nos encontramos, si en modo supervisor o usuario. Existen registros que tan sólo podrán modificarse en modo supervisor.[SIMRM]

#### 3.3.1 REGISTROS DE CONFIGURACIÓN SIM

Este bloque funcional se encarga del control de la configuración de todo el microcontrolador. A continuación se describen los registros de configuración del Módulo SIM que nos interesan, el SIMCR [SIMRM], porque allí se activa/desactiva el modo supervisor y el Módulo de Mapeado, bits que nos interesa controlar, y el SYNCR [SIMRM], para la configuración del reloj del sistema.

#### SIMCR - REGISTRO DE CONFIGURACIÓN DE SIM

Controla la configuración del sistema, puede ser leído y escrito en cualquier momento.

| 15    | . 14  | 13    | 12 | 11    | 10 | 9   | 8 | 7      | 6  | 5 | 4 | 3 | 2   | 1 | 0 |

|-------|-------|-------|----|-------|----|-----|---|--------|----|---|---|---|-----|---|---|

| EXOFF | FRZSW | FRZBM | 0  | SLVEN | 0  | SHE | V | SUPV 1 | им | 0 | 0 | ı | ARB |   |   |

| 0     | 1     | 1     | 0  | 0     | 0  | 0   | 0 | 1      | 1  | 0 | 0 | 1 | 1   | 1 | 1 |

SUPV = 1, los registros con acceso controlado por este bit están restringidos. Solo pueden ser accedidos en modo supervisor.

MM =1, los registros internos se encuentran direccionados desde la posición de memoria \$FFF000 hasta la \$FFFFFF.

IARB = \$F = '1111', es la más alta prioridad, permite la arbitración de interrupciones del mismo nivel que se provoquen a la vez. Este valor evita que interrupciones provocadas en la SIM durante la inicialización sean descartadas.

#### SYNCR – CLOCK SYNTHESIZER CONTROL REGISTER

Determina la frecuencia de operación del reloj del sistema así como su modo de funcionamiento.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4     | 3     | 2     | 1     | 0     |

|----|----|----|----|----|----|---|---|------|---|---|-------|-------|-------|-------|-------|

| W  | Х  |    |    | Υ  |    |   |   | EDIV | 0 | 0 | SLIMP | SLOCK | RSTEN | STSIM | STEXT |

| 1  | 1  | 0  | 1  | 1  | 1  | 1 | 1 | 0    | 0 | 0 | 0     | 1     | 0     | 0     | 0     |

Cuando el 'sintetizador de reloj' es utilizado, los bits del [15:8] del SYNCR determinan la frecuencia de operación.

determinan la frecuencia de operación. Fsystem = Freference[4 (Y+1)( $2^{2W+X}$ )]=32768[4(31+1)( $2^{2\cdot1+1}$ )]=33.554432 MHz SLIM = 0, 'Limp Mode Status', el microcontrolador se encuentra operando en modo normal.

SLOCK = 1,'Synthesizer Lock', VCO se encuentra en la frecuencia deseada o el reloj del sistema es externo.

RSTEN = 0, 'Reset Enable', pérdida de memoria de las causas por las que el microcontrolador actúa en modo 'limp'.

STSIM = 0,'Stop Mode Sim Clock', el 'SIM clock' generado por la referencia externa se apaga cuando nos encontremos en modo de bajo consumo. STEXT = 0, 'Stop Mode External Clock', el CLKOUT se pondrá a 'low' cuando ocurra una parada en el modo de bajo consumo.

#### 3.4 Time Processor Unit (TPU)

La TPU [TPURM] es un inteligente, semiautónomo coprocesador diseñado para el control del tiempo. Opera simultáneamente con la CPU, la TPU procesa microinstrucciones, programas y procesos de eventos hardware en tiempo real, se encarga de la 'entrada' y 'salida', y accede a datos compartidos sin la intervención de la CPU. Consecuentemente, por cada prueba del temporizador hardware, el 'CETUR' de la CPU y el tiempo de servicio son minimizados o eliminados.

El módulo TPU incluye el microcódigo de un conjunto de funciones preprogramadas en ROM.

#### 3.4.1 ESTRUCTURA TPU

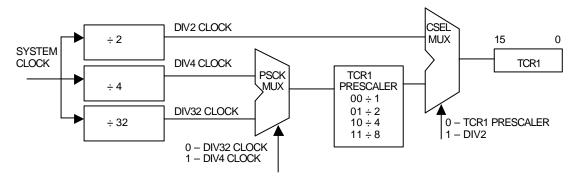

El módulo TPU consiste en 2 contadores de 16 bits, dieciséis canales independientes temporizados, un programador de tareas, un 'microengine' y un 'host interface'. Dos contadores de 16 bits que son tiempos base referencia para todas el 'output compare' e 'input capture events'. Factores de escala que controlan estas dos bases de tiempos a través del registro TPUMCR. MaRTE OS utilizará el factor de escala TCR1, que siempre deriva del reloj del sistema.

La TPU tiene 16 canales independientes, cada uno conectado a un pin del microcontrolador. Los canales tienen idéntico hardware con excepción del canal 15. Cada canal consiste e un registro de evento y un pin de control lógico. El registro de evento contiene un registro de captura de 16 bits, un registro comparador, un comparador 'mayor o igual que' de 16 bits. La dirección de cada pin, si entrada o salida, es determinada por el microcódigo de la TPU.

El 'host interface' permite al CPU 'host' controlar la operación de la TPU. El host CPU debe inicializar la TPU escribiendo en el apropiado registro de interfaz del host para asignar una función, nivel de interrupción, y prioridad de cada canal.

El CPU host hace a un canal activo cuando a éste le asigna una de las prioridades: alta, media o baja. El programador de tareas determina el orden en

el que los canales son atendidos basados en número de canal y la prioridad asignada.

El 'microengine' esta compuesto por un control de almacenaje y una unidad de ejecución. En el 'control-store ROM' se guarda el microcódigo de cada función mascarada. [TPURM]

#### 3.4.2 REGISTROS DE CONFIGURACIÓN TPU

A continuación se hace referencia a los registros de configuración de la TPU. [TPURM]

TPUMCR - TPU MODULE CONFIGURATION REGISTER

| 15   | 14  | 13  | 12  | 11 | 10  | 9    | 8     | 7    | 6      | 5     | 4    | 3   | 2  | 1 | 0 |

|------|-----|-----|-----|----|-----|------|-------|------|--------|-------|------|-----|----|---|---|

| STOP | TCR | N1P | TCR | 2P | EMU | T2CG | STF : | SUPV | PSCK T | PU2 T | 2CSL | IAF | RB |   |   |

| 0    | 0   | 1   | 1   | 1  | 0   | 1    | 0     | 0    | 1      | 0     | 0    | 1   | 1  | 1 | q |

De este registro nos interesa lo siguiente

STOP = 0, 'Stop Bit' la TPU opera con normalidad.

TCR1P = '0 1', 'Timer Count Register 1 Prescaler Control', MaRTE OS utiliza este.

SUPV = 0,'Supervisor Data Space', los registros asignables son accesibles tanto como usuario como supervisor.

PSCK = 1, 'Prescaler Clock', system clock/4 es la entrada del prescaler TCR1

TPUMCR2 - TPU MODULE CONFIGURATION REGISTER 2

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7       | 6      | 5 | 4   | 3  | 2 | 1         | 0 |  |

|-----|----|----|----|----|----|---|------|---------|--------|---|-----|----|---|-----------|---|--|

| 0 0 |    | 0  | 0  | 0  | 0  | 0 | DIV2 | SOFTRST | ETBANK |   | FPS | CK |   | T2CF DTPU |   |  |

| 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0       | 0      | 0 | 0   | 0  | 0 | 0         | 0 |  |

DIV2 = 0, Divide by 2 Control, el TCR1 Incrementa la frecuencia determinada por los campos TCR1 y PSCK.

Así que el registro TCR1 se incrementará cada:

$(33554432 \text{ Hz} \div \text{DIV4} \div \text{TCR1P})^{-1} = (33554432 \text{ Hz} \div 4 \div 2)^{-1} = 238.41 \text{ ns}$

#### 3.4.3 INTERRUPCIONES TPU

La CPU compara el nivel de cada petición de interrupción que recibe con el valor de la máscara de interrupción. Las peticiones de interrupción de niveles mayores que el de la máscara son aceptadas; Los niveles menores o iguales al valor de la máscara son ignorados. La excepción a la norma es el nivel 7 de petición de interrupción no mascarable, el cual es aceptado y dado servicio incluso si las máscara de interrupción de la CPU es 7.

Todos los periféricos que se encuentren implementados en el chip tienen asignados un nivel de petición de interrupción de 0 a 7. Siete es la más alta prioridad, uno es la más baja, y 0 deshabilita cualquier petición de interrupción.

El nivel de petición de interrupción de canal se encuentra en el registro de configuración de interrupciones de la TPU.

Para estar seguros de donde debe buscar la CPU la rutina de servicio de interrupción para cada tipo de interrupción está el CIBV (Channel Interrupt Base Vector) que determina donde encontrar las 16 rutinas de interrupción que puede servir la TPU, una para cada uno de los 16 canales de la TPU. CIBV es el *nibble*, cada una de las mitades de una palabra de 8 bits, más significativo del número del vector de interrupción en tamaño byte; el nibble menos significativo es el propio numero de canal. CIBV debería contener un número de vector que no esté reservado.

La CPU puede enmascarar interrupciones para los canales de forma individual en el CIER (Channel Interrupt Enable Register). Un cero en un bit de este registro enmascara la interrupción de un canal específico, un uno habilita la interrupción en ese canal. Si la interrupción del canal se encuentra enmascarada, podemos leer el registro CISR (Channel Interrupt Status Register), si el canal tiene pendiente la petición de interrupción.

#### TICR – TPU INTERRUPT CONFIGURATION REGISTER

| 15        | 14 | 13 | 12 | 11 | 10 | 9    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|----|----|----|----|----|------|---|---|---|---|---|---|---|---|---|

| 0 0 0 0 0 |    |    |    | 0  |    | CIRL |   |   |   |   |   |   |   |   |   |

| 0         | 0  | 0  | 0  | 0  | 1  | 0    | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

CIRL ='100', 'Channel Interrupt Request Level, estos tres bits especifican el nivel de petición de interrupción para todos los canales de la TPU. El nivel siete en este campo indicaría interrupción no mascarable; nivel cero indicaría que todos los canales de interrupción están desactivados.

CIBV = '0101', 'Channel Interrupt Base Vector, la TPU tiene asignado únicamente dieciséis vectores de interrupción, un vector para cada canal. Este campo específica el 'nibble' más significativo de los números de los vectores que son asignados como vectores de interrupción. El 'nibble' menos significativo viene dado por el número de canal.

Para saber en que posición de memoria va a buscar la CPU la rutina manejadora de interrupciones se debe hacer el siguiente cálculo:

Dir. Vector interrupción = 4 x nº vector interrupción + dirección del VBR

VBR – Vector Base Register, se encuentra en la posición de memoria \$0, es un registro de la CPU32 que contiene los vectores de excepción. Para más información *Reference Manual MC68332*.

Por ejemplo, si CIBV = \$5 y canal 1, la dirección de memoria donde se debería encontrar la rutina de interrupción de este canal será \$51 x \$ = \$144

#### CIER - CHANNEL INTERRUPT ENABLE REGISTER

| 15   | 14   | 13   | 12     | 11     | 10    | 9    | 8    | 7     | 6     | 5     | 4    | 3    | 2    | 1     | 0 |

|------|------|------|--------|--------|-------|------|------|-------|-------|-------|------|------|------|-------|---|

| CH15 | CH14 | CH13 | CH12 ( | CH11 ( | H10 C | H9 C | H8 C | H7 CI | H6 CH | 15 C⊦ | 4 CH | 3 CH | 2 CH | 1 CHO | ) |

| 0    | 0    | 0    | 0      | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0    | 0    | 0    | 0     | 0 |

En la inicialización todos los canales deben tener deshabilitadas las interrupciones, requisito de MaRTE OS. En este registro se habilitan las interrupciones de la TPU individualmente.

0 – interrupción deshabilitada

1 – interrupción habilitada

#### CISR - CHANNEL INTERRUPT STATUS REGISTER

| 15   | 14   | 13     | 12     | 11     | 10    | 9    | 8     | 7     | 6     | 5     | 4    | 3    | 2    | 1     | 0 |

|------|------|--------|--------|--------|-------|------|-------|-------|-------|-------|------|------|------|-------|---|

| CH15 | CH14 | CH13 ( | CH12 ( | CH11 ( | H10 C | H9 C | H8 CI | H7 CI | 16 CH | 15 C⊦ | 4 CH | 3 СН | 2 CH | 1 CHC | ) |

| 0    | 0    | 0      | 0      | 0      | 0     | 0    | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0     | 0 |

Este registro indica algún canal de la TPU ha provocado interrupción. No debe haber interrupciones pendientes durante la inicialización, requisito de MaRTE OS.

0 – interrupción no se ha producido

1 – se ha producido interrupción

#### CFSR# - CHANNEL FUNCTION SELECT REGISTER

| 15   | 14   | 13       | 12 | 11   | 10  | 9       | 8   | 7    | 6    | 5     | 4   | 3    | 2    | 1       | 0   |

|------|------|----------|----|------|-----|---------|-----|------|------|-------|-----|------|------|---------|-----|

| CHAN | INEL | 15,11,7, | 3  | CHAN | NEL | 14,10,6 | 6,2 | CHAN | INEL | 13,9, | 5,1 | CHAN | INEL | . 12,8, | 4,0 |

| #    | #    | #        | #  | #    | #   | #       | #   | #    | #    | #     | #   | #    | #    | #       | #   |

El '#' corresponde a 0, 1,2 ó 3. Dependiendo del canal que se quiera utilizar.

El valor que se puede asignar a cada canal corresponde es un valor de 4bits que corresponderá a una de las funciones predefinidas en la TPU ROM. Ver Pág. 56 de *TPU Reference Manual*.

# HSQR#-HOST SEQUENCE REGISTER